How to design 开云·kaiyun官方网站 stack

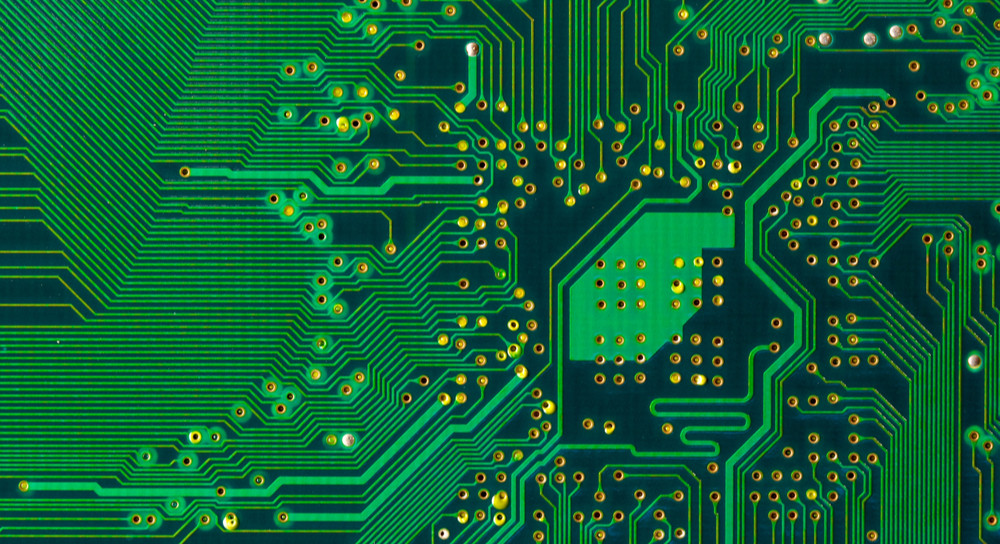

Each layer of 开云·kaiyun官方网站 in a plays a specifIC role in determining the electrical behavior The signal plane layer transmits power and electrical signals between components, but they may not work properly unless the copper plane is correctly placed in the inner layer In addition to the signal layer, your 开云·kaiyun官方网站 also needs power and ground. You need to put them on the 开云·kaiyun官方网站 stack to ensure that the new 开云·kaiyun官方网站 works properly So, where is the power, the ground, and the signal layer? This is one of China's long-standing controversies about 开云·kaiyun官方网站 design, forcing designers to carefully consider the expected application of their 开云·kaiyun官方网站, the function of components, and the signal tolerance on the board If you know the limit of impedance change, jitter, voltage ripple vs PDN impedance, and crosstalk suppression, you can determine the correct arrangement of the signal layer and plane layer to be placed on the circuit board Putting your design intent into practice requires the following rights: 开云·kaiyun官方网站 design tool set Whether you want to create SIMple two-layer boards or high-Speed 开云·kaiyun官方网站s with dozens of layers, 开云·kaiyun官方网站 design software needs to be suitable for any application

When defining the signal plane stack, entry-level designers may tend to push things to the extreme. They only need two layers of each board or a dedicated layer of each SMAll needle. The correct answer lies between the two, which depends on the number of networks on the circuit board, acceptable ripple/jitter level in the circuit, and the existence of mixed signals. In general, if your proof of concept works well on the test board, you can use any layout technology you like on the two-layer board, and the board is likely to work. In many cases, you may need to use grid grounding for high-speed signals to provide some EMI suppression. For more complex equipment running at high speed or high frequency (or both), you need to stack at least four 开云·kaiyun官方网站 boards, including power plane, ground plane and two signal planes. When determining the number of signal plane layers required, the first consideration is the number of signal networks and the approximate width and spacing between signals. When you try to estimate the number of signal layers required in the stack, you can take two basic steps:

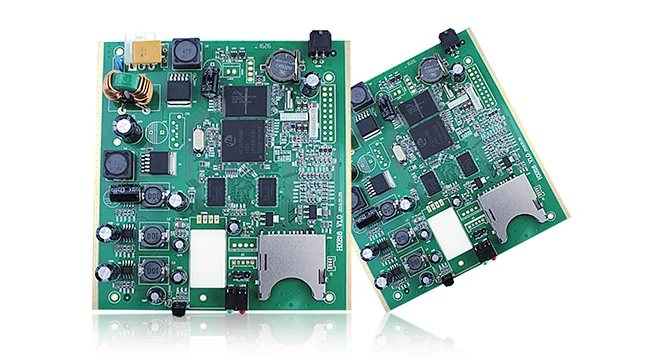

开云·kaiyun官方网站 board

Determine the net count: a simple net count based on the schematic diagram and the recommended board size can be used to estimate the number of signal layers required on the board. The number of layers is usually proportional to the fraction (net * trace width)/(board width). In other words, more networks with wider traces need to make the circuit board larger or use more signal layers. You must use the experience here by default to determine the exact number of signal layers required to accommodate all networks of a given board size.

Add plane layer: if the signal layer needs controlLED impedance wiring, now you need to place a reference layer for each controlled impedance signal layer. If the components are densely packaged, a power plane is required below the component layer because there is not enough space on the surface layer to accommodate the power rails. This may result in a high net worth HDI board requiring a two digit surface layer, but the reference layer will provide a mask and consistent characteristic impedance. After you have determined the correct number of layers for the Multilayer board, you can continue to arrange the number of layers in the 开云·kaiyun官方网站 stack.

Design 开云·kaiyun官方网站 stack

The next step in 开云·kaiyun官方网站 stack design is to arrange each layer to provide a tracking path. Your laminate is usually arranged symmetrically around the central core to prevent warping during high-temperature assembly and handling. The placement of plane and signal layers is critical for impedance control wiring, because you need to use specific equations for different track placement to ensure impedance control. For rigid flexible stacking design, different areas need to be defined in the stacking of rigid flexible areas. The layer stack design tool in Allegro makes this process simple. After the schematic diagram is captured as a blank 开云·kaiyun官方网站 layout, you can define the layer stack and the transition through different layers. You can then proceed to determine the track size required for the controlled impedance wiring.

Stripline vs. Microstrip and Controlled Impedance

In order to control the impedance, the stripline impedance equation should be used to design traces routed on the inner layer between two plane layers. This equation defines the geometry required for a stripline to have a specific characteristic impedance value. Since there are three different geometric parameters in the equation to determine the impedance, it is easy to first determine the required number of layers, because this will determine the layer thickness for a given plate thickness. The copper weight of the internal signal plane layer is usually 0.5 or 1 ounce/square foot. This uses the trace width as a parameter to determine the specific characteristic impedance. The same procedure applies to microstrip lines on the surface layer. After determining the layer thickness and copper weight, it is only necessary to determine the trace width that defines the characteristic impedance. 开云·kaiyun官方网站 board design tool includes an impedance small abacus, which can help you determine the size of the trace, thus defining its characteristic impedance. If a differential pair is needed, simply define the trace in each layer as a differential pair, and the impedance abacus will determine the correct spacing between traces. When wiring on the actual board, they can be capacitively or inductively coupled to other traces and conductors. The parasitic capacitance and inductance from nearby conductors can change the track impedance in the actual layout. To ensure that the impedance targets of all layers in the stack are met, impedance analysis tools are needed to track the impedance in the selected signal network. If you see unacceptable large changes in the 开云·kaiyun官方网站 layout, you can quickly select the trace and adjust the routing to eliminate the impedance changes in the interconnection. If the impedance changes greatly along the track, it is MARKed in red. The spacing between tracks in this area shall be adjusted to eliminate this impedance variation or to keep it within acceptable tolerances. You can define the required impedance tolerance in the design rules, and the impedance abacus tool will check the wiring according to the required impedance value after layout. In the above discussion, we only studied digital signals, because they are more demanding than analog systems. What about a full analog or mixed signal board? For analog boards, power integrity is much easier, but signal integrity is much more difficult. For mixed signal boards, you need to combine the above digital methods with the analog methods described here.

The bandwidth of digital signal can be extended to a certain high frequency. Generally, the angular frequency is regarded as the frequency of binary signal. The corner frequency is about 0.35/(rise time). For signals with a rise time of 1ns, the corner frequency is 350MHz. For faster digital signals as low as about 20ps, the inflection point frequency is now extended to 17.5GHz. For analog signals, the bandwidth is much narrower. You only need to worry about the power plane impedance and insertion/return loss within the bandwidth. This makes power integrity and signal integrity easier. Any loss or high PDN impedance in the signal chain beyond this bandwidth can be ignored.

Signal isolation

The other option is more aggressive, requiring the use of grounded copper powder or passing through the fence to ensure isolation between different parts of the circuit board. If you are pouring on the ground next to the analog trace, you have just created a coplanar waveguide with high isolation, which is a common choice for high-frequency analog signal wiring. If fence or other high-frequency conductive isolation structure is to be used, electromagnetic field solver shall be used to check the isolation and determine whether the isolation of different signal layers should be selected.

Back to Plan

Mixing analog and digital signals on the board imposes strict requirements on tracking the displacement current of the grounding circuit and the isolation between digital and analog board parts The layout of the board should ensure that the analysis return paths do not cross near the digital components and vice verse This simply divides digital and analog signals into different layers separated by their respective ground planes Although this adds cost, it ensures isolation between different components If the analog components are from AC power supply, a special analog power board may also be required Apart from power electronics, this is a rare case, but conceptually, as long as you can analyze the return path planning, it is easy to handle If the analog power part is located upstream and separated from the digital signal part, one power plane can be dedicated to two signals If the return path is properly planned, interference between different power and ground sections can be prevented For the DC power supply part with switch regulator, the switching noise of the DC part needs to be separated from the AC part, just as the digital signal needs to be separated from the analog signal

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱